(Para una perspectiva general de la historia y la actualidad de la tecnología microelectrónica, recomiendo la lectura de «Microelectrónica. La historia de la mayor revolución silenciosa del siglo XX«; 2018, Ediciones Complutense)

Dentro de una sala limpia de fabricación de circuitos integrados

Como estamos viendo en los últimos meses, el mundo sufre una fuerte escasez de chips que está afectando a numerosas industrias, principalmente a la del automóvil, muy dependiente de esa tecnología. He explicado en otros artículos las razones inmediatas y de fondo de esa escasez. Una de las causas es que hay muy pocos fabricantes en el mundo capaces de hacer lo que podemos denominar los chips de vanguardia. Y eso se debe, entre otras razones a la extraordinaria complejidad que significa fabricar uno de tales chips. En este artículo explico una de las causa de esta complejidad: la necesidad de conectar adecuadamente entre sí miles de millones de transistores de un tamaño similar a un virus. Verán que el asunto es casi ciencia ficción. En el siguiente vídeo pueden irse haciendo una idea de esto:

El primer dato que debemos conocer es cuántos transistores hay en un chip de vanguardia. Dependiendo del fabricante, ese número podemos situarlo en el entorno de 100 millones de transistores en cada mm2 de chip. Sí, ha leído bien el dato. Siempre que se dan estos datos surge la pregunta obvia: ¿Por qué queremos tener cada vez más transistores? Tener más transistores en un área dada significa que los circuitos se pueden hacer más pequeños, lo que ahorra costes, o significa que se pueden añadir más funciones a un chip sin tener que agrandarlo.

La industria microelectrónica nos ha acostumbrado desde sus inicios a pensar que el avance no se detiene, que no hay límites, que cuando aparecen las dificultades, se superan con cierta facilidad porque es consustancial a esta industria encontrar soluciones cada vez más asombrosas e imaginativas a los problemas. Pero ahora, con la industria de los chips estamos llegando, literalmente, al borde del abismo, porque como dice el título de este artículo, se están quedando sin nanómetros. ¿Qué va a hacer la industria cuando se traspase la barrera <1 nm? La pregunta es muy pertinente y hay una sombra en el horizonte que amenaza con convertirse en un verdadero cuello de botella: ¿Cómo se interconectan entre sí los miles de millones de transistores reseñados? Veamos cuáles son los problemas y sus posibles soluciones.

1. El problema de las interconexiones en los chips

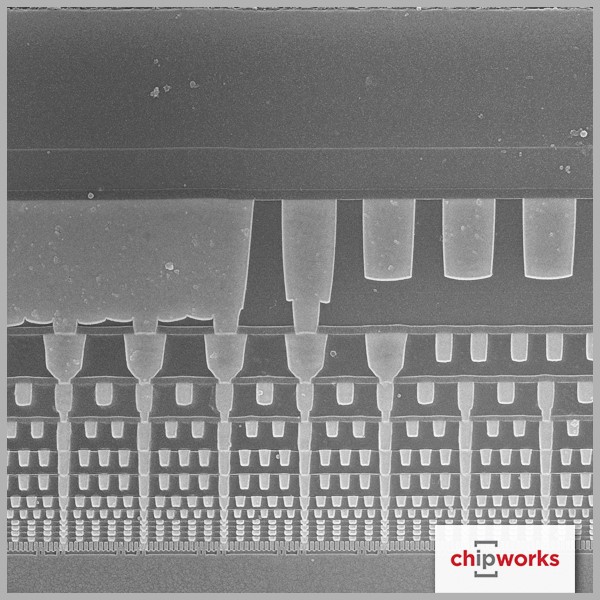

El problema es el siguiente: cada transistor tiene tres terminales y todos deben conectarse correctamente para lograr que el chip realice las funciones determinadas para las que se diseñó. Cuando el número es tan descomunal, necesitamos varios “pisos” de vías metálicas para lograr el objetivo, lo que es un verdadero desafío, porque las pistas de interconexión deben conectar solo los terminales necesarios y deben estar bien aislados de otras conexiones para evitar cortocircuitos no deseados. La imagen muestra un esquema en corte transversal, que ilustra el concepto de lo que realmente hay detrás de una interconexión ¿Y qué ocurre cuando el número de transistores se dispara?, pues pasa lo que se ve en la siguiente imagen:

Esquema en corte transversal de un chip en el que hay cinco “pisos” o niveles de metalización. Los transistores están en la “planta baja” de la imagen (señalada con la sigla FEOL) y las conexiones con el mundo exterior, en la “azotea” (el “back-end”). Cada material de los que se usan para fabricarlos está especificado en el cuadro de la parte superior derecha

La figura anterior ilustra qué ocurre al interconectar tantos transistores: necesitamos varios niveles de interconexión, en los que hay pistas metálicas aisladas entre sí mediante capas aislantes para evitar cortocircuitos, lo que en el mundillo se conoce como “multilevel interconexión”, paradigma vigente desde hace 25 años, cuando lo puso en marcha IBM. Como se puede ver, los transistores están en la primera capa del chip, “enterrados” en un sinfín de capas. Lo que IBM introdujo fue, por una parte, el multilevel y por otra, la sustitución del aluminio para conectar las capas de los chips por el cobre, ya que este material conduce la electricidad mejor que el aluminio, pero con un 40% menos de resistencia, mejorando con ello el rendimiento de cada chip, ya que se disipa mucha menos potencia en las interconexiones, al ser la resistencia que presentan al paso de la corriente inferior.

El problema al que se enfrentan los fabricantes de chips en los nodos de 5 nm e inferiores es el siguiente: a medida que el número de transistores crece, las pistas de interconexión deben hacerse cada vez más delgadas y es aquí donde empiezan los problemas: una pista metálica presenta cada vez mayor resistencia al paso de la corriente eléctrica cuanto más delgada se hace. A su vez, si tenemos cada vez más transistores interconectados con pistas cada vez más delgadas el problema se desboca. Voy a explicar esto con más detalle:

En esencia, fabricar un chip consta de tres partes claves: los transistores, los contactos entre terminales o “patas” y las interconexiones al mundo exterior:

- Los transistores, según hemos visto en la imagen anterior, están en la parte inferior del chip

- Los contactos entre transistores conectan todos los transistores entre sí, a través de diferentes pisos o capas. Un chip actual está formado por no menos de 10 capas, con un máximo que, por ahora, no supera 15 capas, así que cuando vemos un chip en realidad lo que vemos es la última de las capas de metalización, los transistores nunca se ven, salvo que realicemos un corte transversal y lo miremos con un microscopio electrónico de barrido. Lo veremos en el próximo punto.

- Las interconexiones del chip al mundo exterior, es decir, a la placa base de un ordenador, un teléfono móvil, un GPS, etc.

Para ilustrar las casi infinitas complejidades que introducen las interconexiones: la longitud total de las interconexiones de un dispositivo actual suponen cerca de 4.000 km. distribuidos por una superficie que, dependiendo del chip, oscila en el margen 4-10 cm2. Para 2024, esa cifra podría llegar a 14.000 km.

Cada capa tiene que ser conectada con la inferior y ahí radica todo el problema de la industria de chips actuales, en el concepto de conexión e interconexión entre todo lo que forma el chip en sí.

2. ¿Estamos llegando, una vez más, al límite?

¿Cómo se realiza el proceso de conexión entre los terminales de cada transistor a las diferentes partes de un chip? El problema es que, al reducir el tamaño de los transistores, cada capa de conexión entre ellos, que según el “piso” de metalización se denominan FEOL (Front-End-Of-the-Line) (la de contacto con los transistores), MOL (Middle-Of-Line) (los pisos intermedios) y BEOL (Back-End-Of-Line) (las últimas) tienen que ser más robustas, deben tener menor resistencia al paso de la corriente y deben tener unas dimensiones cada vez más reducidas, en consonancia con la reducción del tamaño de los transistores y esos requisitos son incompatibles entre sí: menor resistencia al paso de corriente entra en contradicción con menos tamaño de las interconexiones. La imagen, esta vez real, lo ilustra:

Imagen tomada por micorscopía electrónica de un corte transversal de un chip Broadwwll de Intel, fabricado en tecnología de 14 nm. Se muestran las 13 capas de interconexión. A medida que los diseños de chips se encogen, las capas de metal se vuelven más complicadas

Al reducir el tamaño de cada transistor, conectar las primeras capas (FEOL) con las últimas (BEOL) requiera de nuevos materiales que permitan una conductividad eléctrica y térmica igual o mejor en un espacio entre capas que es cada vez más pequeño. Reducir transistores en escala nanométrica implica tener que reducir lo que se denomina el “Metal Pitch”, parámetro que mejor define en la actualidad el tamaño real de cada transistor en el chip:

Ilustrando el concepto de “Metal Pitch”, mide la separación entre los contactos a las regiones externas de un transistor, denominadas Drenador y Fuente

En cualquier caso, son conexiones cada vez más pequeñas, en particular también las vías que conectan entre sí diversos pisos, lo que añade dificultades a la hora de “rellenarlas” adecuadamente, que a su vez implica menos metal para rellenarlos y así interconectar capas, lo que acarrea mayor resistencia al paso de la corriente y precisamente aquí está el problema y el reto. El cobre está dejando de ser el material de referencia, porque con un Metal Pitch por debajo de 30-40 nm se vuelve totalmente inestable para conducir corriente con la velocidad y precisión que se necesita. En otras palabras, se pueden tener transistores con unas dimensiones de pocos nanómetros, pero si no se pueden conectar con el metal apropiado, no se puede fabricar un chip sin pérdidas, fugas o rupturas eléctricas, lo que dispara el consumo o directamente lo vuelve impracticable en la realidad.

En la actualidad, parece que el Cobalto o el Rutenio podrían ser sustitutos viables para el cobre, pero utilizando técnicas que, hoy por hoy, son desconocidas o no suficientemente probadas. En todo caso, este es uno más de los desafíos a los que se enfrenta la industria microelectrónica en los próximos 2-3 años. Sin la menor duda, esta industria seguirá deparándonos sorpresas e imaginación, como hace cada vez que un nuevo obstáculo aparece en el horizonte.