⚠️ El desafío de los 1.000 pisos de memoria: ¿hasta dónde puede llegar el apilamiento en 3-D NAND?

🎯 La industria empuja con fuerza hacia memorias 3-D NAND con más de 800 capas, buscando llegar a nada menos que 1.000 capas, para satisfacer la insaciable demanda de capacidad. Pero esta escalada vertical no solo aumenta el espacio, también multiplica los retos técnicos.

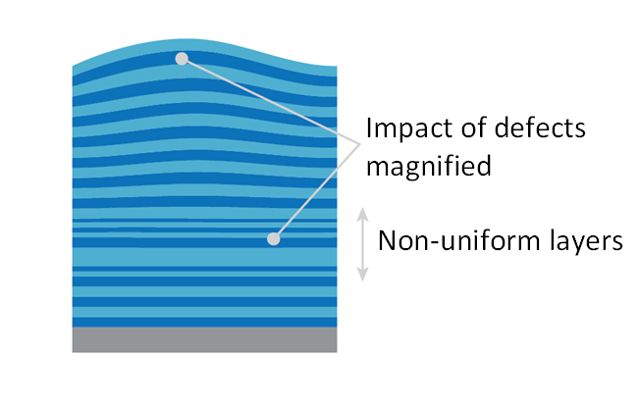

🎯 Uniformidad y planaridad al límite: cada capa extra añade errores de planitud que se acumulan y se vuelven críticos en pilas más altas. Empresas como ACM Research están implementando técnicas como rotar la oblea 180° durante la deposición, alcanzando una uniformidad de apenas el 1 % de variación.

🎯 Dificultades en el grabado (etching): perforar columnas verticales con proporciones de altura-ancho cercanas a 100:1 agrava problemas como grabados desalineados, variaciones en dimensiones críticas y deformaciones laterales. Se requieren hard masks más robustos, y se están explorando materiales alternativos como recubrimientos “spin-on” para mejorar rendimiento y productividad.

🎯 Limpieza y secado extremos: una vez grabadas las columnas profundas, eliminarlas es complejo. Se usan agitación ultrasónica para introducir fluidos limpiadores y CO₂ supercrítico para secar sin dañar estructuras críticas.

🚀 Reto del canal «Macaroni»: la estructura concéntrica del canal, con silicio policristalino, empieza a limitar la corriente de lectura conforme aumenta la altura del stack. Una solución explorada es el canal de monocristal mediante crecimiento epitaxial o cristalización asistida por silicio metálico, aunque ambas opciones implican costos y complejidad técnica: desde procesamiento a alta temperatura hasta el uso de dos obleas y unión híbrida, ganando rendimiento pero duplicando costos y residuos.

⚠️ Esto es una llamada de atención sobre cómo la innovación tecnológica se encuentra cara a cara con los límites físicos. Es un recordatorio de que escalar en 3-D no es solo apilar, es dominar materiales, procesos y arquitectura.

👉 Si quieres leer más: https://lnkd.in/djTYvmV7

El desafío de los 1.000 pisos de memoria: ¿hasta dónde puede llegar el apilamiento en 3-D NAND?